Next-Generation Submodule Technology for MMC

-

its scalability,

- no need for passive filters,

- low di/dt of the arm currents,

- low switching frequency, and

- direct and fast control of the AC and DC side.

In previous projects, MMC have basically been equipped with Half-Bridge Submodules due to the minimum expenditure of semiconductors and therefore low losses. The disadvantage of Half-Bridge Submodules on the other hand is no possibility for electronic DC-current limitation at converter level (regarding unipolar terminal voltage) and high volume submodule capacitors.

Future requirements for MMC at system level are therefore the:

- reduction of submodule capacitor volume,

- applying submodule topologies with bipolar terminal voltage to enable DC-current limitation and cut-off by the MMC itself (what results in the redundancy of DC circuit breakers), and

- enabling electronic protection of submodules against explosion.

The future requirements should concurrently not lead to increased converter losses.

The Double-Zero Submodule (DZ-SM)

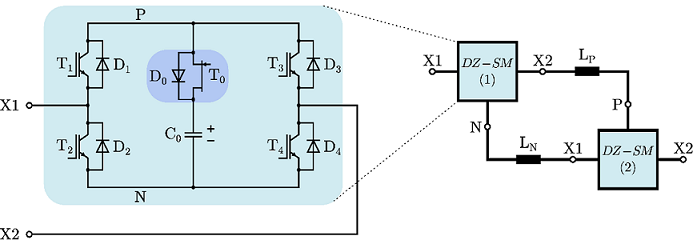

By introducing a controllable DC-capacitor – realized by a reverse conducting SiC-FET – a novel control scheme becomes possible, enabling reduced on-state losses and reduced switching losses. In addition, a double submodule circuit (DZ-DC-SM) can be realized by external connection of two single DZ-SM.

Fig. 1: Double-Zero submodule (DZ-SM) and double connection of two DZ-SM (DZ-DC-SM)

The features of this novel topology in double connection are:

- reduced on-state losses,

- reduced capacitor size,

- lossless capacitor balancing,

- electronic protection against explosion, and it is

- well adapted for SiC-FET.

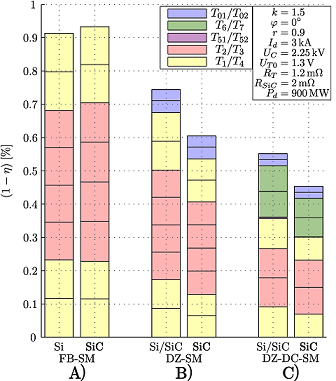

The most promising submodules are investigated, in order to analyze the individual on-state power loss of the different semiconductors:

- series connection of two Full-Bridge submodules (FB-SM)

- series connection of two Double-Zero submodules (DZ-SM)

- Double-Zero submodule in double connection (DZ-DC-SM).

The left bar graphs in B) and C) are depicting submodules as a mixture of Si-HV-IGBT and SiC-FET semiconductor devices as a next technological step, where a fully Si-HV-IGBT-version of the conventional FB-SM is utilized as a reference in A). By comparison, fully SiC-FET equipped submodules are presented in the right bar graphs.

It can be noted, that the on-state losses of the Double-Zero submodule (B)) can be significantly reduced, where the full potential of loss reduction will be achieved with a fully SiC-FET equipped submodule. In the case of the double connection (C)), further 25% loss reduction can be achieved – cutting the total on-state loss in half compared to the conventional Full-Bridge submodule topology.

Fig. 2: Normalized total power losses per submodule in a typ. HVDC-MMC application

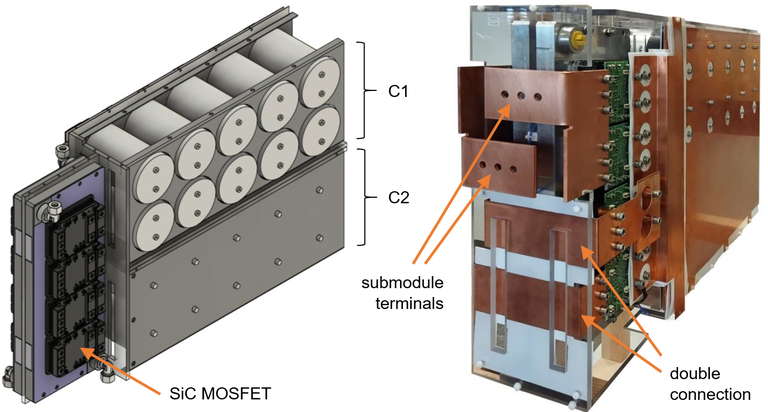

A lab prototype of the DZ-DC-SM is implemented based on 3.3-kV SiC MOSFETs, with two 2-kV, 2.05-mF capacitor banks. The submodule delivers terminal voltages of +4 kV, +2 kV, 0 kV, and -2 kV and is rated for arm currents of 500-600 A. The use of cylindrical capacitors allows an especially slim design and very low inductive commutation paths. The dimensioning of the semiconductors has been primarily focused on high efficiency targets at nominal load. In MMC of double-star configuration it enables a semiconductor efficiency of up to 99.8 % (assuming a switching frequency of 150 Hz per double submodule).

Fig. 3: DZ-DC-SM prototype implementation based on 3.3-kV SiC MOSFETs

- A. Sharaf Addin, R. Marquardt, and T. Brückner, “Design of a compact low-loss MMC double submodule for MVDC and HVDC applications,” in Proc. IEEE-APEC, Atlanta, GA, USA, 2025.

- A. Sharaf Addin, C. Dahmen, and T. Brückner, “Extended balancing and dimensioning of capacitors in MMC double submodules,” in EPE'22 ECCE Europe, Hannover, Germany, 2022.

- C. Dahmen and R. Marquardt, “Ultra low loss - MMC submodules favorable for SiC-FET enabling high functional safety,” in EPE'22 ECCE Europe, Hannover, Germany, 2022.

- C. Dahmen and R. Marquardt, “Reduced capacitor size and on-state losses in advanced MMC submodule topologies,” in EPE'20 ECCE Europe, Lyon, France, 2020.

-

C. Dahmen and R. Marquardt, “Power losses of advanced MMC submodule topologies using Si-and SiC-semiconductors,” in EPE '19 ECCE Europe, Genova, Italy, 2019.